| Abstract                                |     |

|-----------------------------------------|-----|

| Introduction                            |     |

| Development environment                 |     |

| Development process                     | 5   |

| Components                              | 6   |

| Overall view                            | 7   |

| Counter                                 | 7   |

| rs232 recv                              | 7   |

| rs232 recv shift register               | 7   |

| rs232 multiplex                         | 8   |

| img_input                               | 8   |

| life input                              |     |

| app ctrl                                |     |

| rs232 send                              |     |

| rs232 send shift register               |     |

| rs232_send_byte                         |     |

| mem tester                              |     |

| led simple display                      |     |

| led_ascii_display                       |     |

| vga                                     |     |

| vga controly                            |     |

| vga controlh                            |     |

| lfsr                                    |     |

| vga ram                                 |     |

| vga shift register                      |     |

| life ram                                |     |

| basic cell                              |     |

| large cell                              |     |

| ram swap                                |     |

| mem controller                          |     |

| life                                    |     |

| Problems encountered during development |     |

| Testing the system                      |     |

| Possible improvements                   |     |

| Conclusion                              |     |

| References                              |     |

|                                         |     |

| VHDL Source Code                        |     |

| app_ctrl.vhdbasic_cell.vhd              |     |

|                                         |     |

| counter.vhd                             |     |

| img_input.vhd                           |     |

| large_cell.vhd                          |     |

| led_ascii_display.vhd                   |     |

| led_simple_display.vhd                  |     |

| lfsr.vhd                                |     |

| life.vhd                                |     |

| life_input.vhd                          |     |

| life ram.vhd                            | .26 |

| mem_controller.vhd            | 30 |

|-------------------------------|----|

| mem tester.vhd                | 33 |

| ram_swap.vhd                  | 35 |

| rs232 multiplex.vhd           | 35 |

| rs232_recv.vhd                | 37 |

| rs232_recv_shift_register.vhd |    |

| rs232_send.vhd                |    |

| rs232 send byte.vhd           | 41 |

| rs232 send shift register.vhd | 42 |

| vga.vhd                       | 43 |

| vga controlh.vhd              |    |

| vga controlv.vhd              |    |

| vga ram.vhd                   |    |

| vga shift register.vhd        |    |

## **Abstract**

This report describes our work as part of the project oriented course "Advanced Digital Design" taught at EPFL. We designed a VGA controller and three demonstration applications. The first application is very simple and displays a "snow" effect based on random pixels (something resembling what a TV set displays when there is no signal). The second application allows us to display a simple color image on the screen. The third application runs the famous game of life. We also designed a unit for bi-directional communication with a PC using the serial port.

The goal of this course was to provide us with an overview of what the challenges are when developing a large hardware project.

We synthesized our project for an Altera VHDL (FPGA) board and connected a normal computer monitor to show our results.

## Introduction

The graphics card is the hardware that allows a computer to display images on a screen. The screen is represented in memory as a large set of pixels. Each pixel has a red, green and blue component. The graphics card is responsible to transmit these pixels through analog signals. VGA is a standard used to transmit this data to the screen. It was marketed by IBM in 1987. The VGA specifications are a screen size of 640 by 480 pixels and the colors are encoded as 0V - 0.7V (actually the specification is much more complex, describes palette modes, etc.). Although the VGA standard is very low resolution, it is the common denominator of all graphics card.

For detailed information on the VGA controller, please refer to the course's handout (VGA.pdf).

The famous game of life is a cellular automaton (invented in 1970 by John Conway). It is a topic broadly studies in computer sciences and mathematics. We will only give a vague explanation on how the game works, without going into the details. The game of life is "played" on a rectangle board, where each cell can be either alive (set to 1) or dead (set to 0). Every cycle, each cell changes it's state depending on it's current value and the state of it's 8 neighboring cells. The rules of the game state that if a cell is alive and has more than 3 neighbors or less than 2 neighbors then it will die, otherwise it will survive. If the cell is dead and has 3 neighbors, then it will take birth. The fun part in the game of life is to find initial patterns that do interesting things. Once the initial pattern is loaded, the user doesn't interact with the world (he just looks at the evolution of his pattern).

For more detailed information on the game of life, refer to the course's handout (GameOfLife.pdf).

In order to create the initial pattern, we wrote a Java user interface that communicates with the FPGA through the serial port (RS232).

See UART.pdf.

## **Development environment**

We used the hardware description language VHDL to program all the hardware components. We used ModelSim to compile and simulate our code. We then used Leonardo to synthesize the code and Quartus to perform the routing and FPGA programming. We suggest using Teraterm as the terminal emulator to communicate with the card, as we had some problems with Hyperterm.

The development board used was Altera's Excalibur series. The board contains the EP20K200EFC484-2X FPGA, which has 200.000 gates and 106.496 bits of memory.

For debugging purpose we used the 7 segment leds on the card and various types of switches and buttons.

The card also has a RAM of 64K x 32 bits. This RAM is used to store the image or game of life state. Most modern graphics controllers have simultaneous read/write RAMs. Unfortunately, it wasn't the case for us, so we had to make sure to never read and write at the same time. The calculation of the life states therefore needs to be interlaced with the screen rendering.

## **Development process**

The project was divided into 4 assignments. Since we didn't need to hand in each assignment, we weren't forced to follow the course's guidelines. Here is how we worked:

At first we wrote the RS232 controller. We thought that it would be a wise idea to implement bi-directional communication, since it didn't involve a lot of extra work. It turns out, this saved us a lot of debugging time later on. We then wrote the VGA related code. The VGA controller is actually much simpler than the word sounds (people are always impressed when you tell them you made a graphics card from scratch). To test the VGA controller we created an image renderer. This involved creating a memory controller to store and read from the RAM. Each pixel of the image is stored as 4 bits, the first bit is ignored, the next bits represent the red, green and blue components. This means we can only display up to 8 colors. This limitation is due to the amount of RAM we have, and also due to the digital-analog converter that we have (a simple diode) that generates either 0V or 0.7V based on the digital input signal (that is either 0V or 5V).

We then implemented the game of life. Our game of life is 640 by 480 cells (each cells corresponds to one pixel on the screen) and the top-bottom, right-left are wrapped. This involved extending the memory controller. The life pattern is saved as 1 bit per cell value, but the pattern is saved twice in memory, because it's much easier to calculate the next generation of cells without erasing the current generation's values (since the game is wrapped) and then swapping memory regions. Our game of life runs at the screen refresh rate (60 Hz).

When transferring data to the board, the first byte specifies if we want to display an image (first byte = 0x02), in which case we must transfer 153601 bytes, or the game of life (first byte = 0x01) in which case we must transfer must send 38401

bytes. This is handled by a multiplex we added to the rs232 code.

One of our design goals (which wasn't stated in the hand out) was to design the system in such a way that we can retransmit a new life pattern or a new image at any time. We have achieved this at the cost of some extra complexity and time investment.

We finally implemented a hardware pseudo-random number generator just for the fun of doing it. We used a technique known as linear feedback shift register (lfsr). We won't go into the mathematical details (which involve galois fields and Fibonacci numbers) of this random generator. We used this random number generator to display the "snow" effect while transferring data to the board.

Note: It was said during our lectures that it is impossible to go beyond 640x480 cells or 60Hz. We would like to point out here that this is not impossible. We could have created a larger grid and used buttons to scroll the display. We could have also calculated more generations per screen refresh (which would mean we would be running faster than 60Hz, but not displaying every generation). A third interesting option would have been to link two cards together and have the game run on two screens (with gliders going from one screen to the other). If time had permitted us, we would have probably tried this crazy idea.

## Components

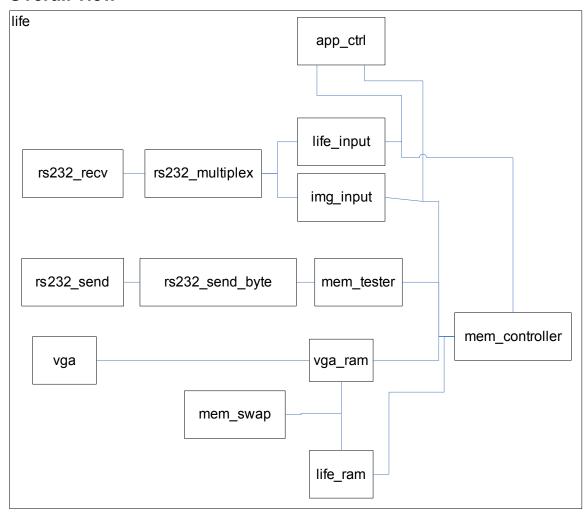

Our project is based on several independent components. See figure on following page for an overall view. We will present the components from the simplest to the most complex (hence the more interesting components are presented last). The most important components are the following:

- life.vhd This component is the top most and ties everything together.

- basic\_cell.vhd Calculates the future state of a cell given the cell and it's 8 neighbors.

- vga.vhd Generates the VGA signals.

- app\_ctrl.vhd Controls which application is currently running and generates a signal (sync\_counter) which is used to synchronize the VGA with the game of life.

- mem\_controller.vhd This part controls the RAM. It allows, in a very flexible manner, for every component to safely perform a read or a write access.

#### Overall view

#### Counter

This is a very fundamental component. For simplicity we designed one counter that we reused throughout the project (10 bits counter). We could have designed individual counters (or used the generic type in VHDL) to save bits, but we consider the advantage of ease of development to be worth the extra few bits. The counter's value is saved in a register and is presented to the outside world (signal value). Every clock cycle, if the inc input signal is set, then the counter value is incremented until it matches data. When the counter reaches data, it raises the timeout signal and reset's itself.

Note: the data (target value) isn't saved in a register.

## rs232\_recv

# rs232 recv shift register

Shift registers are another fundamental components in our system. We have different shift registers, since we needed different types each time. The rs232\_recv\_shift\_register takes a single bit as input and generates 8 output bits. The shift happens only when the shift signal is set.

Note: We didn't provide any reset option, since we don't need it (we know that we will always be reading the dataout signal after 8 bits have been pumped in).

The rs232\_recv component is used to read data from the serial port. Like many other more complex components, it is based on a state machine. It uses two counters, one to keep track of the 115200 bauds rate and one to remember how many bits of data have been read.

The rs232\_recv component raises the rs232\_recv\_ack signal when it has received 8 bits of data. For an understanding of how the state machine works, refer to UART.pdf.

## rs232\_multiplex

This component is very basic, it allows for the multiplexing of the game of life with the image renderer. It is connected to rs232\_recv. It starts out in the idle state, and looks at the first byte (a byte = 8 bits) that the rs232\_recv gets. If the byte is 0x01, then it will set itself into life mode. If the byte is 0x02, then it will set itself into img mode. Otherwise it will stay in idle mode. Remember we stated one of our design goals was to be able to reload images and life patterns. In order for that to happen, the rs232\_multiplex must know when the last byte of data has arrived. This happens by receiving a done signal from the life\_input or img\_input components. Again this component is very generic and could be extended to multiplex with other applications.

## img\_input

## life\_input

The objective of these components is to receive the data from rs232\_multiplex to which they are connected, and to save the data at the right place in memory. The actual memory access is performed in mem\_controller (see below). So all these components do is generate the memory address and raise a signal (img\_input\_done and life\_input\_done) when the data has finished arriving. The RAM is accessed by 32 bits at a time (we can read or write 32 bits at a time). So here is how we laid out the memory:

- For the images, the 9 bits of the row are concatenated to the 7 bits of the col. The last 3 bits of the col are used to select one pixel (remember a pixel is stored as 4 bits) among 8 in the 32 bits.

- For the game of life, the top most bit controls which part in ram we want to access (remember we are swapping between two regions). The second bit is always 0. The next 9 bits are the row and the following 5 bits come from the col (higher 5 bits). 5 col bits (lower 5 bits) are used to select a cell among the 32 bits.

## app\_ctrl

This component tells the other components (through the mode signal) which application is running and generates a signal used to synchronize the VGA with the game of life. The state is defined as two bits, "00" means we are transferring

data on the rs232 (and the VGA must thus display the "snow" effect), "01" means we are in the game of life mode and "11" means we are displaying an image. The synchronization signal is a counter from 0 to 31 in the case of the game of life and a counter from 0 to 8 in the case of the image display mode.

This component uses the rs232\_recv\_ack signal to know when the application goes back to waiting for rs232 data to finish transferring.

## rs232\_send

## rs232\_send\_shift\_register

This component performs the reverse operation of the rs232\_recv\_shift\_register. It takes as input 8 bits and shifts 1 bit out whenever the shift signal is set.

The rs232\_send component is very similar to the rs232\_recv component. It uses counters and rs232\_send\_shift\_register to output data to the serial port.

## rs232\_send\_byte

This component is a helper component that will take a byte and send it using the rs232\_send component. It will then notify (by raising byte\_send\_done) that the data has gone.

## mem\_tester

This is another helper component, it will use rs232\_send\_byte to dump part of the memory on the serial port.

# led\_simple\_display

A very simple component to display data on the leds.

## led\_ascii\_display

A similar component, but takes as input the ascii value of a digit and displays the corresponding digit on the 7 segment leds (it maps a digit to the right bit pattern).

## vga

# vga\_controlv

# vga\_controlh

These components generate the hsync and vsync signals, as described in the specification (refer to VGA.pdf). The vga\_controlh also generates signals to tell when to increment the vga\_controlv.

This component puts vga\_controlh and vga\_controlv together. It also generates the col and row values that are used by vga\_ram to load and display the right pixels at the right time.

#### lfsr

This component generates a pseudo-random sequence of bits. It's used by vga\_ram to display random pixels on the screen.

## vga\_ram

## vga\_shift\_register

This component is used to postpone the hsync and vsync signals by 32 or 8 clock cycles. We must do this in order to have enough time to load data from the RAM before sending both, the pixels and sync signals to the monitor.

This is among the most complex components in our system. Basically it loads data from the RAM (either 8 pixels or 32 cells) based on the current row and col values into a register. The register is then used to display these pixels on the screen, but in such a way that we send the pixel either exactly 8 or 32 clock cycles. By doing this we make sure that the pixels correspond to the sync signals, but also we make sure that the register get overridden exactly when the last pixel has been displayed.

This component is responsible for sending black pixels when the VGA is in either horizontal sync or vertical sync.

When in life mode, the vga\_ram will load the data from the ram at the cycle 30 and 31. This means all the other cycles can be freely used by life\_ram to read and store data.

## life\_ram

## basic cell

Performs the basic game of life computation.

Note: the future state isn't saved in a register, nor is the current state. The registers are actually in the life\_ram component. This component is therefore purely combinatory.

# large\_cell

This component allows us to compute 32 life cells at the same time. Since the RAM is read/written 32 bits at a time, we found it to be a good design decision to calculate the life cells in chunks of 32 bits.

This is the second complex component in our system. It basically performs 9 load requests (each load takes 1 cycle) and then waits one cycle (so that basic\_cell is done it's calculation) and then writes back the data (writing data takes 3 cycles). Since each load and write also takes an extra cycle due to the structure of mem\_controller, that means we calculate 32 cells in 23 clock ticks. Since VGA uses clock cycles 30 and 31, we don't do anything with the remaining 7 clock cycles. If you calculate the amount of time needed to calculate an entire generation of life, you will find a value much smaller than the amount of time

needed to update the entire screen; so this implies we have a lot of extra cycles that we can "waste" wherever it is convenient.

The computation starts over again after a memory swap has happened.

#### ram\_swap

This component controls when the ram can be swapped. The rules are the following: the mode must be life, the screen must be in the vertical sync state and the computation of the life is idle.

## mem\_controller

This is the third complex component in our system. The RAM access is controller here. The mem\_controller is connected to the following 5 components: life\_input (for writing), img\_input (for writing), life\_ram (for reading and writing), vga\_ram (for reading) and mem\_tester (for reading).

The mem\_controller checks who wants to access the RAM and grants it based on the following priority rule (from greatest priority to lowest):

img\_input > life\_input > life\_ram\_load > mem\_tester > life\_ram\_save > vga\_ram

This priority is only for debugging purpose. There is actually never any conflict since the ram and life are synchronized by app\_ctrl. However the mem\_controller generates an ack signal to the component it has granted access. This means we can change our memory access policy and we could tell vga\_ram and life\_ram to try accessing the ram until they are granted to do so. This implies the vga\_ram would become even more complicated because we would have to manage the case when the component isn't granted access and must therefore maintain a cache.

#### life

This is the top most component. All it does is tie all the other components together.

# Problems encountered during development

The first problem which we had was related to the rs232 rx signal. We had learned in other courses that signals coming from the outside should go through a series of cascading D flip-flops. This should be done to avoid setting the system in a meta-stable state. At first we thought that we wouldn't need these flip-flops because we know the rate at which the rx signal varies. This is indeed true, but we don't know when the first rx change will occur, and this can set our entire rs232 circuit into a meta-stable state. We therefore added two levels of flip-flops. There is no rule as to how many levels to have, probabilistic laws say that the more levels you add, the less likely you are to have a meta-stable state (the risk of having a meta stable state is never 0!).

The second problem we had was related to the buttons on the board generating multiple transitions (due to the mechanical design of the buttons). We solved this problem by required alternating between two buttons (this is relevant only to our debugging process).

The third problem we had was related to the VHDL language. It turns out the tools we had wouldn't raise a warning if we wrote something like: if (signal <= some\_value) then

This simple mistake took us some time to find, and once we realized our tools were too liberal regarding the language, we wrote a perl script to find such mistakes. It would be great if the VHDL related tools could detect common programming mistakes.

# **Testing the system**

In order to test the system, you must load the life.sof file using Quartus and then launch our Java GUI:

java -Xms256m -Xmx256m -classpath "comm.jar;jiu.jar;." GUI

As you can see we used the comm API (Sun) for transferring data over the serial port and JIU (Java Imaging Utility) to manipulate images (different methods for reducing number of colors, image resizing).

Note: As of the writing of this document, the java code wasn't fully functional.

# **Possible improvements**

There are many things we could have improved, had we had enough time:

- Better documentation of the code we wrote.

- More technical details in this document.

- Written a generic counter to save bits.

- Written a generic shift register to save in number of files.

- Implement the full rs232 protocol (with handshaking, ack and parity checking).

## Conclusion

To end this report, all we can say is we had a lot of fun doing hardware development. We were able to meet the requirements very quickly, and we were also able to extend our project without too much trouble. What is very amazing is that we were able to work as a team of two students without any problems. Usually hardware development is more difficult in teams, probably because one small mistake can break everything, but this wasn't at all the case in our team.

## References

We used the lecture slides and notes, mainly the following files:

- UART.pdf

- VGA.pdf

- DescriptionRam.pdf

- SimulationAfter.pdf

- ManuelOutilsFPGA.pdf

- CarteAltera.pdf

- GameOfLife.pdf

## **VHDL Source Code**

## app\_ctrl.vhd

```

-- app_ctrl.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

library ieee;

use ieee.std_logic_1164.all;

use ieee.std logic arith.all;

entity app ctrl is

port (

clk, reset: in std logic;

-- 00 this signal will set the system in rs232

rs232_recv_ack: in std_logic;

life input done, img input done: in std logic;

-- 01 this signal will set the

system in life mode.

-- 11 this signal will set the

system in img mode.

mode: out std logic vector(1 downto 0);

sync_counter: out std_logic_vector(9 downto 0)); -- this counter is used to sync the

vga with life.

end app ctrl;

architecture synth app ctrl of app ctrl is

component counter is

port(clk: in std logic;

reset: in std logic;

inc: in std_logic;

data: in std logic vector(9 downto 0);

timeout: out std_logic;

value: out std_logic_vector(9 downto 0));

end component;

signal current_state, next_state: std_logic_vector(1 downto 0);

signal counter data: std logic vector(9 downto 0);

signal ctrl reset, counter timeout: std logic;

begin

process(current state)

begin

if (current state = "11") then

counter_data <= conv_std_logic_vector (7, 10);</pre>

counter data <= conv std logic vector(31, 10);</pre>

end if;

end process;

counter_unit: counter port map (clk => clk, reset => ctrl_reset, inc => '1', data =>

timeout => counter timeout, value => sync counter);

mode <= current state;</pre>

process (clk, reset)

begin

if (reset = '1') then

current state <= "00";

elsif (clk'event and clk='1') then

current state <= next state;

end if;

end process;

process(current state, reset, rs232 recv ack, life input done, img input done)

begin

ctrl reset <= reset;

if (rs232_recv ack = '1') then

next_state <= "00";

elsif (life_input_done = '1') then

ctrl_reset <= '1';

next_state <= "01";

elsif (img_input done = '1') then

ctrl reset <= '1';

```

```

next state <= "11";</pre>

else

next state <= current state;</pre>

end if;

end process;

end synth_app_ctrl;

basic cell.vhd

-- basic cell.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

library ieee;

use ieee.std_logic_1164.all;

use ieee.std logic unsigned.all;

entity basic_cell is

port(nw, n, ne, e, se, s, sw, w, m: in std logic;

next state: out std logic);

end basic cell;

architecture synth basic cell of basic cell is

signal temp1 : std_logic_vector(1 downto 0);

signal temp2 : std logic vector(1 downto 0);

signal temp3 : std logic vector(1 downto 0);

signal temp4 : std_logic_vector(2 downto 0);

signal sum : std logic vector(3 downto 0);

begin

temp1 <= ('0' & nw) + ('0' & n) + ('0' & ne);

temp2 <= ('0' & e) + ('0' & se) + ('0' & s);

temp3 <= ('0' & sw) + ('0' & w);

temp4 <= ('0' & temp1) + ('0' & temp2);

sum <= ("00" & temp3) + ('0' & temp4);

process(m, sum)

begin

next state <= '0';</pre>

if (sum="0011") then

next state <= '1';</pre>

-- 3 neighbours means birth or survival (m=0 or

elsif(m='1' and sum="0010") then

next state <= '1';</pre>

-- 2 neighbours means birth (iff m=1)

end if:

end process;

end synth basic cell;

counter.vhd

-- counter.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This unit is a "generic" (it's not that generic,

-- because it always uses 10 bits) counter. It

-- counts from 0 to data. When it reaches data, it

-- raises the timeout signal and resets itself on

-- the next clk rise.

-- The counter only counts when the inc input signal

-- is set.

-- Note: the data is not kept in a register (there is

no load signal), so it must always be set by

the unit using the counter.

-- Value is the counter's current value.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std logic arith.all;

use ieee.std logic unsigned.all;

entity counter is

```

```

port(clk: in std logic;

reset: in std logic;

inc: in std logic;

data: in std logic vector(9 downto 0);

timeout: out std logic;

value: out std logic vector(9 downto 0));

end counter;

architecture synth counter of counter is

signal reg: std logic vector(9 downto 0);

process(reset, clk)

begin

if (reset='1') then

reg<=(others => '0');

timeout <= '0';

elsif (clk'event and clk='1') then

if (inc='1') then

if (reg = data) then

timeout <= '1';</pre>

else

timeout <= '0';

end if:

if (reg = data) then

reg<=(others => '0');

else

reg <= reg + conv std logic vector(1, 9);</pre>

end if;

else

timeout <= '0';

end if;

end if;

end process;

value <= reg;</pre>

end synth counter;

```

## img\_input.vhd

```

-- life input.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- Three counters are used, to keep track of the col/row and

-- when to write.

^^^^^

-- row (0-479) => 9 bits

-- col (0-1024) => 7 most significant bits

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic arith.all;

use ieee.std_logic_unsigned.all;

entity img input is

port(clk: in std_logic;

reset: in std logic;

-- rs232

img recv ack: in std logic;

img_recv_data: in std_logic_vector(7 downto 0);

img input write req: out std logic;

img_input_write_ack: in std_logic;

img_input_addr: out std_logic_vector(15 downto 0);

img_input_data: out std_logic_vector(31 downto 0);

img input done: out std logic);

end img_input;

architecture synth_img_input of img input is

component counter is

port (clk: in std logic;

reset: in std logic;

inc: in std_logic;

```

```

data: in std logic vector(9 downto 0);

timeout: out std logic;

value: out std logic vector(9 downto 0));

end component;

signal byte timeout, col timeout, row timeout: std logic;

signal byte_value, col_value, row_value, byte_data, col_data, row_data :

std logic vector(9 downto 0);

{\tt component rs232\_input\_shift\_register is}

port (clk: in std logic;

datain: in std_logic_vector(7 downto 0);

shift: in std logic;

dataout: out std logic vector(31 downto 0));

end component;

begin

byte data <= conv std logic vector(3, 10);</pre>

col_data <= conv_std_logic_vector(79, 10);

row_data <= conv_std_logic_vector(479, 10);</pre>

byte counter: counter port map (clk => clk, reset => reset, inc => img recv ack, data =>

timeout => byte timeout, value => byte value);

col counter: counter port map (clk => clk, reset => reset, inc => byte timeout, data =>

timeout => col timeout, value => col value);

row counter: counter port map (clk => clk, reset => reset, inc => col timeout, data =>

row_data,

timeout => row timeout, value => row value);

shift reg: rs232 input shift register port map (clk => clk, datain => img recv data,

shift => img recv ack, dataout => img input data);

img_input_addr <= row_value(8 downto 0) & col_value(6 downto 0);</pre>

img input done <= row timeout;</pre>

img_input_write_req <= byte timeout;</pre>

end synth img input;

large cell.vhd

-- large cell.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_arith.all;

use ieee.std logic unsigned.all;

entity large cell is

port(n, m, s: in std_logic_vector(33 downto 0);

newgen: out std logic vector(31 downto 0));

end large cell;

architecture synth large cell of large cell is

component basic cell is

port(nw, n, ne, e, se, s, sw, w, m : in std_logic;

next state : out std logic);

end component;

Life32: for i in 1 to 32 generate

life32_map: basic_cell port map(m \Rightarrow m(i), nw \Rightarrow n(i-1),

n \Rightarrow n(i), ne \Rightarrow n(i+1), e \Rightarrow m(i+1), se \Rightarrow s(i+1)

+1), s => s(i),

sw \Rightarrow s(i-1), w \Rightarrow m(i-1), next state \Rightarrow

newgen(i-1));

end generate Life32;

end synth_large_cell;

led_ascii_display.vhd

-- led ascii display.vhd

```

```

-- This unit is for debugging purpose. It

-- allows us to display ascii decoded digits.

-- Valid values are currently 0 (ascii 48=0x30) to

-- 9 (ascii 57=0x39).

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std logic unsigned.all;

s0

-- s s

--

3 5

s1

-- s s

-- 4 6

s2

.s7

entity led ascii display is

port(data: in std_logic_vector(6 downto 0);

leds: out std_logic_vector(6 downto 0));

end led ascii display;

architecture synth led ascii display of led ascii display is

begin

process (data)

begin

case data is

when "0000000" => -- clr

leds(0) <= '1'; leds(1) <= '1'; leds(2) <= '1'; leds(3) <= '1';

leds(4) <= '1'; leds(5) <= '1'; leds(6) <= '1';

when "0110000" => -- 0

leds(0) <= '0';

leds(3) <= '0';

leds(5) <= '0';

leds(1) <= '1';

leds(4) <= '0';

leds(6) <= '0';

leds(2) <= '0';

when "0110001" => -- 1

leds(0) <= '1';

leds(3) <= '1';

leds(5) <= '0';

leds(1) <= '1';

leds(4) <= '1';

leds(6) <= '0';

leds(2) <= '1';

when "0110010" => -- 2

leds(0) <= '0';

leds(3) <= '1';

leds(5) <= '0';

leds(1) <= '0';

leds(4) <= '0';

leds(6) <= '1';

leds(2) <= '0';

when "0110011" => -- 3

leds(0) <= '0';

leds(3) <= '1';

leds(5) <= '0';

leds(1) <= '0';

leds(4) <= '1';

leds(6) <= '0';

leds(2) <= '0';

when "0110100" => -- 4

leds(0) <= '1';

leds(3) <= '0';

leds(5) <= '0';

leds(1) <= '0';

leds(4) <= '1';

leds(6) <= '0';

leds(2) <= '1';

when "0110101" => -- 5

leds(0) <= '0';

leds(3) <= '0';

leds(5) <= '1';

leds(1) <= '0';

leds(4) <= '1';

leds(6) <= '0';

leds(2) <= '0';

when "0110110" => -- 6

leds(0) <= '0';

leds(3) <= '0';

leds(5) <= '1';

leds(1) <= '0';

leds(4) <= '0';

leds(6) <= '0';

leds(2) <= '0';

when "0110111" => -- 7

```

```

leds(0) <= '0';

leds(3) <= '1';

leds(5) <= '0';

leds(1) <= '1';

leds(4) <= '1';

leds(6) <= '0';

leds(2) <= '1';

when "0111000" => -- 8

leds(0) <= '0';

leds(3) <= '0';

leds(5) <= '0';

leds(1) <= '0';

leds(4) <= '0';

leds(6) <= '0';

leds(2) <= '0';

when "0111001" => -- 9

leds(0) <= '0';

leds(3) <= '0';

leds(5) <= '0';

leds(1) <= '0';

leds(4) <= '1';

leds(6) <= '0';

leds(2) <= '0';

when others => -- err

leds(0) <= '0';

leds(3) <= '0';

leds(5) <= '1';

leds(1) <= '0';

leds(4) <= '0';

leds(6) <= '1';

leds(2) <= '0';

end case;

end process;

end synth led ascii display;

```

## led\_simple\_display.vhd

```

-- led_simple_display.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This unit is for debugging purpose. It

-- allows us to display 7 bits on the

-- 7 segment leds

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

s0

-- s s

-- 3 5

s1

-- s s

-- 4 6

s2

.s7

entity led_simple_display is

port(data: in std_logic_vector(6 downto 0);

leds: out std logic vector(6 downto 0));

end led_simple_display;

architecture synth_led_simple_display of led_simple_display is

leds <= data;</pre>

end synth led simple display;

```

#### Ifsr.vhd

```

-- lfsr.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- Hardware pseudo-random number generator

-- based on the linear feedback shift register technique.

-- This implementation is based on 8 bits and provides

-- a random bit pattern of length 255. The tab used is

-- 0,1,2,7

library ieee;

```

```

use ieee.std logic 1164.all;

use ieee.std_logic_arith.all;

use ieee.std logic unsigned.all;

entity lfsr is

port (

clk, reset: in std logic;

rand: out std logic);

end lfsr;

architecture synth lfsr of lfsr is

signal reg: std_logic_vector(31 downto 0);

signal f: std logic;

begin

process(clk, reset)

begin

if (reset='1') then

reg <= (0 => '1', others => '0');

elsif (clk'event and clk='1') then

reg <= f & reg(31 downto 1);

end if;

end process;

rand <= reg(0);

f \le reg(0) xor reg(3);

end synth lfsr;

life.vhd

-- life.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This is the top most unit of our system.

-- Right now it runs a game of life with the

-- input (game setup) uploaded through the serial port

-- and the display on a 640x480 vga screen.

-- We might support image uploading too.

-- Refer to signals.txt for the mapping of signals

-- from the altera card to the vhdl code.

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_arith.all;

use ieee.std logic unsigned.all;

entity life is

port(clk: in std logic;

nreset: in std logic;

rx: in std logic;

tx: out std_logic;

buttons: in std_logic_vector(3 downto 0);

switches: in std logic vector(7 downto 0);

led1: out std_logic_vector(7 downto 0);

led2: out std_logic_vector(7 downto 0);

ram data: inout std_logic_vector(31 downto 0);

ram_addr: out std_logic_vector(15 downto 0);

ram we: out std logic;

ram_oe: out std logic;

ram0 cs: out std logic;

ram1_cs: out std_logic;

ram0_ble: out std_logic;

ram1 ble: out std logic;

ram0_bhe: out std_logic;

ram1 bhe: out std logic;

r, g, b: out std \overline{logic};

hsync out, vsync out: out std logic);

end life;

architecture synth life of life is

```

component led\_ascii\_display is

end component;

port(data: in std\_logic\_vector(6 downto 0);

leds: out std logic vector(6 downto 0));

```

component led simple display is

port(data: in std_logic_vector(6 downto 0);

leds: out std logic vector(6 downto 0));

end component;

component rs232 recv is

port(clk: in std logic;

reset: in std logic;

rx: in std logic;

rs232_recv_ack: out std_logic;

rs232 recv data: out std logic vector(7 downto 0));

end component;

component rs232_send is

port(clk: in std logic;

reset: in std logic;

tx: out std logic;

rs232 send done: out std logic;

rs232_send_data: in std_logic_vector(7 downto 0);

rs232 sending: in std logic);

end component;

component img_input is

port(clk: in std logic;

reset: in std_logic;

img recv ack: in std logic;

img recv data: in std_logic_vector(7 downto 0);

img input write req: out std logic;

img_input_write_ack: in std_logic;

img_input_addr: out std_logic_vector(15 downto 0);

img input data: out std logic vector(31 downto 0);

img_input_done: out std_logic);

end component;

component life input is

port(clk: in std logic;

reset: in std logic;

life_recv_ack: in std_logic;

life recv data: in std logic vector(7 downto 0);

life_input_write_req: out std_logic;

life_input_write_ack: in std_logic;

life input addr: out std logic vector(15 downto 0);

life_input_data: out std_logic_vector(31 downto 0);

life input done: out std logic);

end component;

component mem_controller is

port(clk: in std logic;

reset: in std logic;

ram data: inout std logic vector(31 downto 0);

ram addr: out std logic vector(15 downto 0);

ram cs: out std logic;

ram we: out std logic;

ram swap: in std logic;

-- \overline{\text{life}} input (WRITE)

life_input_write_req: in std_logic;

life input write ack: out std logic;

life_input_addr: in std_logic_vector(15 downto 0);

life_input_data: in std_logic_vector(31 downto 0);

-- img input (WRITE)

img_input_write_req: in std_logic;

img input write ack: out std logic;

img_input_addr: in std_logic_vector(15 downto 0);

img_input_data: in std_logic_vector(31 downto 0);

-- mem tester (READ)

mem tester read req: in std logic;

mem tester read ack: out std logic;

mem_tester_addr: in std_logic_vector(15 downto 0);

mem_tester_data: out std_logic_vector(31 downto 0);

-- life ram load (READ)

life ram load read req: in std logic;

life_ram_load_read_ack: out std_logic;

life_ram_load_addr: in std_logic_vector(15 downto 0);

life ram load data: out std logic vector(31 downto 0);

-- life ram save (WRITE)

life ram save write req: in std logic;

life ram save write ack: out std logic;

life_ram_save_addr: in std_logic_vector(15 downto 0);

life_ram_save_data: in std_logic_vector(31 downto 0);

-- vga ram (READ)

vga ram read without mem swap: in std logic;

```

```

vga ram read req: in std logic;

vga_ram_read_ack: out std_logic;

vga_ram_addr: in std_logic_vector(15 downto 0);

vga ram data: out std logic vector(31 downto 0);

but2, but3: in std logic);

end component;

component mem tester is

port(clk: in std logic;

reset: in std_logic;

debug start: in std logic;

-- when this signal is set to 1, the mem tester

will start dumping the memory.

mem_tester_read_req: out std_logic;

mem tester read ack: in std logic;

mem tester addr: out std logic vector(15 downto 0);

mem_tester_data: in std_logic_vector(31 downto 0);

byte send done: in std logic;

byte send data: out std_logic_vector(7 downto 0);

byte sending: out std logic);

end component;

component rs232_send_byte is

port(clk: in std logic;

reset: in std logic;

byte send data: in std logic vector(7 downto 0);

byte sending: in std logic;

byte send done: out std logic;

rs232_send_done: in std_logic;

rs232_send_data: out std_logic_vector(7 downto 0);

rs232 sending: out std logic);

end component;

component life ram is

port(clk: in std logic;

reset: in std logic;

-- enable/disable the life calculation -- restart

start: in std logic;

calculation (send from vga_ram

--after the swap has happened)

mode: in std logic vector(1 downto 0);

sync counter: in std logic vector (9 downto 0);

life ram done: out std logic; -- tell the system that the memory can be swapped.

life_ram_load_read_req: out std_logic;

life ram load read ack: in std logic;

life ram load data: in std_logic_vector(31 downto 0);

life_ram_load_addr: out std_logic_vector(15 downto 0);

life_ram_save_write_req: out std_logic;

life_ram_save_write_ack: in std_logic;

life ram save data: out std logic vector(31 downto 0);

life_ram_save_addr: out std_logic_vector(15 downto 0));

end component;

component vga is

port (

clk, reset: in std logic;

hsync, vsync: out std logic;

is_hsync, is_vsync, is_sync: out std logic;

value1, value2: out std logic vector (9 downto 0));

end component;

component vga_ram is

port (

clk, reset: in std logic;

hsync in, vsync in: in std logic;

issync in: in std logic;

col, row: in std logic vector (9 downto 0);

hsync out, vsync out: out std logic;

r, g, b: out std_logic;

vga_ram_read_req: out std_logic;

vga ram read ack: in std logic;

vga_ram_addr: out std_logic_vector(15 downto 0);

vga ram data: in std logic vector(31 downto 0);

vga ram read without_mem_swap: out std_logic;

mode: in std logic vector(1 downto 0);

sync_counter: in std_logic_vector(9 downto 0));

end component;

component ram swap is

port (

clk, reset: in std logic;

is vsync: in std logic;

life ram done: in std logic;

```

```

mode: in std logic vector(1 downto 0);

but4: in std logic;

ram swap: out std logic);

end component;

component app ctrl is

port (

clk, reset: in std logic;

rs232 recv ack: in std logic;

-- 00 this signal will set the system in rs232

recv mode.

life input done, img input done: in std logic;

-- 01 this signal will set the

system in life mode.

mode: out std_logic_vector(1 downto 0);

sync counter: out std logic vector(9 downto 0)); -- this counter is used to sync

the vga with life.

end component;

component rs232 multiplex

port (

clk, reset: in std logic;

rs232_recv_ack: in std_logic;

rs232 recv data: in std_logic_vector(7 downto 0);

life recv ack: out std logic;

life recv data: out std logic vector(7 downto 0);

life done: in std logic;

img recv ack: out std logic;

img recv data: out std logic vector(7 downto 0);

img done: in std logic);

end component;

signal reset: std_logic;

signal life input done, img input done: std logic;

signal life ram done: std logic;

signal but1, but2, but3, but4: std logic;

-- rs232 multiplex

signal life_recv_ack, img_recv_ack: std_logic;

signal life_recv_data, img_recv_data: std_logic_vector(7 downto 0);

-- vga

signal hsync, vsync, is hsync, is vsync, is sync, swap: std logic;

signal value1, value2: std logic vector(9 downto 0);

-- rs232

signal rx1, rx2 : std logic;

signal rs232 recv data, rs232 send data, byte send data: std logic vector(7 downto 0);

signal rs232_recv_ack: std_logic;

signal byte send done, byte sending, rs232 send done, rs232 sending: std logic;

-- mem controller

signal ram cs, ram writeenable: std logic;

signal mem_tester_read_req, mem_tester_read_ack, life_input_write_req,

life input write ack: std logic;

signal img_input_write_req, img_input_write_ack: std logic;

signal life_ram_load_read_req, life_ram_load_read_ack, life_ram_save_write_req,

life ram save write ack: std logic;

signal vga_ram_read_req, vga_ram_read_ack: std_logic;

signal mem tester addr, life input addr, life ram load addr, life ram save addr:

std logic vector(15 downto 0);

signal img_input_addr: std_logic_vector(15 downto 0);

signal mem_tester_data, life_input_data, life_ram_load_data, life_ram_save_data:

std logic vector(31 downto 0);

signal img_input_data: std_logic_vector(31 downto 0);

signal vga ram addr: std logic vector(15 downto 0);

signal vga ram data: std logic vector(31 downto 0);

signal vga ram read without mem swap: std logic;

signal sync counter: std logic vector(9 downto 0);

signal mode: std logic vector(1 downto 0);

-- Solve the problem with the button being active at 1

reset <= not(nreset);</pre>

but1 <= not(buttons(0));</pre>

but2 <= not(buttons(1));</pre>

but3 <= not(buttons(2));</pre>

```

```

but4 <= not(buttons(3));</pre>

-- Solve the problem of rx being an external signal

process(clk, reset)

begin

if (reset = '1') then

rx1 <= '1';

rx2 <= '1';

elsif (clk'event and clk='1') then

rx1 <= rx;

rx2 <= rx1;

end if;

end process;

-- rs232 multiplex

rs232 mutliplex unit: rs232 multiplex port map (clk => clk, reset => reset,

rs232 recv ack => rs232 recv ack,

rs232 recv data => rs232 recv data,

life recv ack => life recv ack,

life recv data => life recv data, life done => life input done,

img recv ack => img recv ack,

img recv data => img recv data, img done => img input done);

-- app ct.rl

app ctrl unit: app ctrl port map (clk => clk, reset => reset, rs232 recv ack =>

rs232_recv_ack,

life input done => life input done, img input done =>

img input done,

mode => mode, sync counter => sync counter);

-- ram swap

ram swap unit: ram swap port map (clk => clk, reset => reset, is vsync => is vsync,

life ram done => life ram done,

mode => mode, ram_swap => swap, but4 => but4);

-- rs232 recv

rs232_recv_unit: rs232_recv port map (clk => clk, reset => reset,

rx => rx2, rs232 recv ack => rs232 recv ack,

rs232 recv data => rs232 recv data);

-- rs232 send

rs232 send unit: rs232 send port map (clk => clk, reset => reset,

tx => tx, rs232_send_done => rs232_send_done,

rs232 send data => rs232 send data, rs232 sending

=> rs232 sending);

-- img input

img_input_unit : img_input port map (clk => clk, reset => reset, img_recv_ack =>

img recv ack, img recv data => img recv data,

img input write req => img input write req,

img input write ack => img input write ack,

img input addr => img input addr, img input data

=> img_input_data,

img input done => img input done);

-- life input

life input unit : life input port map (clk => clk, reset => reset, life recv ack =>

life recv ack, life recv data => life recv data,

life_input_write_req => life_input_write_req,

life input write ack => life input write ack,

life input addr => life input addr,

life_input_data => life_input_data,

life input done => life input done);

-- mem controller

mem controller unit: mem controller port map (clk => clk, reset => reset, ram data =>

ram data, ram addr => ram addr,

ram cs \Rightarrow ram cs, ram we \Rightarrow

ram writeenable, ram swap => swap,

img input write req =>

img input write req, img input write ack => img input write ack,

img input addr => img input addr,

img input data => img input data,

life input write req =>

life input write req, life input write ack => life input write ack,

life input addr => life input addr,

life input data => life input data,

mem tester read req =>

mem_tester_read_req, mem_tester_read_ack => mem_tester_read_ack,

```

```

mem tester addr => mem tester addr,

mem tester data => mem tester data,

life ram load read req =>

life ram load read req, life ram load read ack => life ram load read ack,

life ram load addr => life ram load addr,

life ram load data => life ram load data,

life ram_save_write_req =>

life ram save write req, life ram save write ack => life ram save write ack,

life_ram_save_addr => life_ram_save_addr,

life ram save data => life ram save data,

vga ram read req => vga ram read req,

vga_ram_read_ack => vga_ram_read_ack,

vga ram addr => vga ram addr,

vga ram data => vga ram data,

vga ram read without mem swap =>

vga ram read without mem swap,

but2 => but2, but3 => but3);

ram0 cs <= not(ram cs);

-- active at 0 !

ram1 cs <= not(ram cs);</pre>

ram we <= not(ram writeenable);

ram_oe <= ram_writeenable when ram_cs='1' else '1'; -- oe is selected when cs='1' and

we are not writing.

ram0 ble <= not(ram cs);</pre>

ram0 bhe <= not(ram cs);

ram1_ble <= not(ram cs);</pre>

ram1 bhe <= not(ram cs);

-- game of life

life_ram_unit: life_ram port map (clk => clk, reset => reset, mode => mode,

sync counter => sync counter,

start => swap,

life ram done => life ram done,

life_ram_load_read_req => life_ram_load_read_req,

life ram load read ack => life ram load read ack,

life ram load data => life ram load data,

life ram load addr => life ram load addr,

life ram save write req => life ram save write req,

life ram save write ack => life ram save write ack,

life ram save data => life ram save data,

life ram save addr => life ram save addr);

vga unit: vga port map (clk => clk, reset => reset, hsync => hsync, vsync => vsync,

is hsync => is hsync, is vsync => is vsync, is sync => is sync,

value1 => value1, value2 => value2);

vga ram unit: vga ram port map (clk => clk, reset => reset, hsync in => hsync, vsync in

=> vsync, issync in => is sync,

col => value1, row => value2, hsync out => hsync out,

vsync out => vsync out, r => r,

g => g, b => b, vga ram read req => vga ram read req,

vga ram read ack => vga ram read ack,

vga ram addr => vga ram addr, vga ram data =>

vga ram data, vga ram read without mem swap =>

vga_ram_read_without_mem_swap, mode => mode,

sync counter => sync counter);

-- mem tester

mem tester unit: mem tester port map (clk => clk, reset => reset, debug start => but1,

mem tester read req => mem tester read req,

mem tester read ack => mem tester read ack,

mem tester addr => mem tester addr,

mem tester data => mem tester data,

byte sending => byte sending, byte send data =>

byte send data, byte send done => byte send done);

rs232 send byte unit: rs232 send byte port map (clk => clk, reset => reset,

byte send data => byte send data, byte sending => byte sending,

byte send done => byte send done,

rs232 send done => rs232 send done,

rs232 send data => rs232 send data,

rs232_sending => rs232_sending);

-- led one

led one: led ascii display port map(data => "0001001", leds => led1(6 downto 0));

```

```

led1(7) <= but1;</pre>

-- led two

led two: led ascii display port map(data => "0000110", leds => led2(6 downto 0));

led2(7) <= but2;

end synth life;

life input.vhd

-- life input.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This unit is used to write 32 bits representing

-- 32 pixels from the rs232 into the RAM. life done

-- is raised once 640*480 (after 9600 writes) pixels

-- have been written.

-- Three counters are used, to keep track of the col/row and

-- when to write.

-- The memory is split in two parts, allowing us to read from one

-- part while (we don't read & write at the same time, we just

-- write in one part in order not to overwrite the data needed for the

-- current state) writing in the other, and vice-versa.

ADDR =

0srrrrrrrrccccc

-- which memory to use => 1 bit

-- row (0-479) => 9 bits

-- col (0-1024) \Rightarrow 5 most significant bits

-- Note: the MSB is always 0, so half the memory address space isn't used.

-- This unit depends on

counter

rs232_input_shift_register

-- Note: life input done is not raised at the same time as the

last life ram write (it takes 4 (???) clk ticks to propagate

through the counters)

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic arith.all;

use ieee.std_logic_unsigned.all;

entity life input is

port(clk: in std logic;

reset: in std logic;

-- rs232

life recv ack: in std logic;

life_recv_data: in std_logic_vector(7 downto 0);

life input write req: out std logic;

life_input_write_ack: in std_logic;

life input addr: out std logic vector(15 downto 0);

life input data: out std logic vector(31 downto 0);

life_input_done: out std_logic);

end life input;

architecture synth life input of life input is

component counter is

port (clk: in std_logic;

reset: in std logic;

inc: in std logic;

data: in std logic vector(9 downto 0);

timeout: out std logic;

value: out std logic vector(9 downto 0));

end component;

signal byte_timeout, col_timeout, row_timeout: std_logic;

signal byte_value, col_value, row_value, byte_data, col data, row data :

std logic vector(9 downto 0);

component rs232 input shift register is

port (clk: in std_logic;

```

```

datain: in std logic vector(7 downto 0);

shift: in std logic;

dataout: out std logic vector(31 downto 0));

end component;

begin

byte data <= conv std logic vector(3, 10);

col data <= conv std logic vector(19, 10);</pre>

row_data <= conv_std_logic_vector(479, 10);</pre>

byte counter: counter port map (clk => clk, reset => reset, inc => life recv ack, data =>

byte_data,

timeout => byte timeout, value => byte value);

col counter: counter port map (clk => clk, reset => reset, inc => byte timeout, data =>

col data,

timeout => col timeout, value => col value);

row counter: counter port map (clk => clk, reset => reset, inc => col timeout, data =>

row data,

timeout => row_timeout, value => row_value);

shift_reg: rs232_input_shift_register port map (clk => clk, datain => life_recv_data,

shift => life recv ack, dataout => life input data);

life input addr <= "00" & row value(8 downto 0) & col value(4 downto 0);

life input done <= row timeout;

life input write req <= byte timeout;

end synth life input;

life ram.vhd

-- life ram.vhd

```

```

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This unit is used to load 9 times 32 "pixels" into the large_cell unit

-- calculate the next generation for the 32 pixels, and write

-- the result back into the RAM.

-- In order to keep this unit in sync with the vga code, we must

-- respect a 32 clk cycle.

-- Rules to swap memory:

-- life ram must be done (must be in waiting state)

-- vga must reach bottom of screen

-- If the swap happens then a flag must be set (because the vsync signal

-- lasts for a long time) and the life ram must be aware of it (restart must

-- be set).

library ieee;

use ieee.std_logic_1164.all;

use ieee.std logic arith.all;

use ieee.std_logic_unsigned.all;

entity life ram is

port(clk: in std_logic;

reset: in std logic;

mode: in std logic vector(1 downto 0);

sync_counter: in std_logic_vector(9 downto 0);

start: in std logic;

-- enable/disable the life calculation -- restart calculation (send from vga ram

--after the swap has happened)

-- we need to start signals, one that comes from life (that is used to

-- start when the rs232 finishes but before the first swap, the second

-- to restart once the swap has happened. this is due to the fact that we

-- wanted to be able to debug easily. An alternative would have been

-- to always first swap then calculate, and the first screen would be

-- wrong but nobody would notice.

life_ram_done: out std_logic; -- tell the system that the memory can be swapped.

life ram load read req: out std logic;

life ram load read ack: in std logic;

life_ram_load_data: in std_logic_vector(31 downto 0);

life ram load addr: out std logic vector(15 downto 0);

life_ram_save_write_req: out std_logic;

life_ram_save_write_ack: in std_logic;

```

```

life ram save data: out std logic vector(31 downto 0);

life_ram_save_addr: out std_logic_vector(15 downto 0));

end life ram;

architecture synth_life_ram of life_ram is

component counter is

port(clk: in std logic;

reset: in std logic;

inc: in std logic;

data: in std logic vector(9 downto 0);

timeout: out std logic;

value: out std_logic_vector(9 downto 0));

end component;

component large cell is

port(n, m, s: in std_logic_vector(33 downto 0);

newgen: out std logic vector(31 downto 0));

end component;

-- we need to convert 9x32 bits into the 3x34 bits that interest us (input for

large cell)

signal tnw, tn, tne, tw, tm, te, tsw, ts, tse: std_logic_vector(31 downto 0);

signal n, m, s: std logic vector(33 downto 0);

signal newgen: std logic vector(31 downto 0);

-- counters

signal col value, row value, col data, row data: std logic vector(9 downto 0);

signal col timeout, row timeout: std logic;

-- we need to calculate or keep track of the previous and next values of the counters

signal rowm1, rowp1, colm1, colp1: std_logic_vector(9 downto 0);

type state is (stopped, paused, waiting, 11, 12, 13, 14, 15, 16, 17, 18, 19, w, r);

signal current_state, next_state : state;

-- CONTROL SIGNALS

signal ctrl_col_inc: std_logic;

signal save_data: state;

signal ctrl reset: std logic;

begin

col data <= conv std logic vector(19, 10);</pre>

col_counter_unit: counter port map (clk => clk, reset => ctrl_reset, inc =>

ctrl_col_inc, data => col_data, timeout => col_timeout, value => col_value);

row_data <= conv_std_logic_vector(479, 10);</pre>

row counter unit: counter port map (clk => clk, reset => ctrl reset, inc =>

col timeout, data => row data, timeout => row timeout, value => row value);

large cell unit: large cell port map (n \Rightarrow n, m \Rightarrow m, s \Rightarrow s, newgen \Rightarrow newgen);

process(clk, reset)

if (reset = '1') then

current state <= stopped;

tnw <= (others => '0'); tn <= (others => '0'); tne <= (others => '0');

tw \le (others => '0'); tm \le (others => '0'); te \le (others => '0');

tsw \le (others => '0'); ts \le (others => '0'); tse \le (others => '0');

elsif (clk'event and clk='1') then

current state <= next state;</pre>

case save data is

when 11 =>

tnw <= life_ram_load_data;</pre>

when 12 =>

tn <= life_ram_load_data;</pre>

when 13 =>

tne <= life ram load data;

when 14 =>

tw <= life ram load data;

when 15 \Rightarrow

tm <= life ram load data;

when 16 =>

te <= life ram load data;

when 17 =>

tsw <= life_ram_load_data;</pre>

when 18 =>

ts <= life_ram_load_data;</pre>

when 19 =>

tse <= life ram load data;

when others \Rightarrow null;

end case;

end if;

end process;

```

```

life ram save data <= newgen;

life ram save addr <= "00" & row_value(8 downto 0) & col_value(4 downto 0);

process(reset, current state, start, mode, sync counter, row timeout,

life ram load read ack, rowm1, colm1, rowp1, colp1, row value, col value)

begin

life ram save write req <= '0';

life_ram_load_read_req <= '0';

life_ram_load_addr <= (others => '0');

ctrl col inc <= '0';

save_data <= paused;

life ram done <= '0';

if (mode = "00") then

next state <= stopped;</pre>

ctrl_reset <= '1';

else

ctrl reset <= reset;

case current_state is

when stopped =>

next state <= waiting;</pre>

when paused =>

-- the default behaviour is to wait for start

to be activated.

life_ram_done <= '1';</pre>

if (start = '1') then

next state <= waiting;

else

next state <= paused;

end if;

when waiting =>

-- wait for sync to happen

if (row timeout = '1') then

-- end of calculation of entire map

next state <= paused;

elsif (sync counter = conv std logic vector(31, 10)) then

next_state <= 11;</pre>

else

next state <= waiting;

end if;

when 11 =>

-- load 9 times 32 pixels.

life_ram_load_read_req <= '1';</pre>

life_ram_load_addr <= "00" & rowm1(8 downto 0) & colm1(4 downto 0);

if (life_ram_load_read_ack = '1') then</pre>

save data <= 11;

next_state <= 12;</pre>

next_state <= 11;</pre>

end if;

when 12 =>

life_ram_load_read_req <= '1';

life_ram_load_addr <= "00" & rowm1(8 downto 0) & col_value(4 downto 0);</pre>

if (life ram load read ack = '1') then

save data <= 12;

next_state <= 13;</pre>

else

next state <= 12;

end if;

when 13 =>

life_ram_load_read_req <= '1';</pre>

life_ram_load_addr <= "00" & rowm1(8 downto 0) & colp1(4 downto 0);

if (life ram load read ack = '1') then

save data \leq 13;

next state <= 14;

else

next_state <= 13;</pre>

end if;

when 14 =>

life ram load read req <= '1';

life_ram_load_addr <= "00" & row_value(8 downto 0) & colm1(4 downto 0);</pre>

```

```

if (life ram load read ack = '1') then

save data <= 14;

next state <= 15;</pre>

next state <= 14;

end if;

when 15 =>

life_ram_load_read_req <= '1';

life_ram_load_addr <= "00" & row_value(8 downto 0) & col_value(4 downto 0);</pre>

if (life ram load read ack = '1') then

save_data <= 15;

next state <= 16;

else

next_state <= 15;</pre>

end if;

when 16 =>

life_ram_load_read_req <= '1';

life_ram_load_addr <= "00" & row_value(8 downto 0) & colp1(4 downto 0);</pre>

if (life_ram_load_read_ack = '1') then

save_data <= 16;

next state <= 17;

else

next state <= 16;

end if;

when 17 =>

life_ram_load_read_req <= '1';

life_ram_load_addr <= "00" & rowp1(8 downto 0) & colm1(4 downto 0);</pre>

if (life_ram_load_read_ack = '1') then

save_data <= 17;

next state <= 18;

else

next state <= 17;

end if;

when 18 =>

life_ram_load_read_req <= '1';

life_ram_load_addr <= "00" & rowp1(8 downto 0) & col_value(4 downto 0);</pre>

if (life ram load read ack = '1') then

save_data <= 18;</pre>

next state <= 19;

else

next state <= 18;

end if;

life_ram_load_read_req <= '1';

life_ram_load_addr <= "00" & rowp1(8 downto 0) & colp1(4 downto 0);</pre>

if (life_ram_load_read_ack = '1') then

save data <= 19;

next_state <= w;

else

next state <= 19;

end if;

when w =>

next_state <= r;</pre>

when r =>

-- and simply write result back in ram

life_ram_save_write_req <= '1';</pre>

ctrl_col_inc <= '1';

next state <= waiting;</pre>

when others => null;

end case;

end if;

end process;

process(tnw, tn, tne, tw, tm, te, tsw, ts, tse)

n(33) \le tnw(0); m(33) \le tw(0); s(33) \le tsw(0);

n(32 \text{ downto } 1) \le tn(31 \text{ downto } 0);

m(32 \text{ downto } 1) \le tm(31 \text{ downto } 0);

s(32 \text{ downto } 1) \le ts(31 \text{ downto } 0);

```

```

n(0) \le tne(31); m(0) \le te(31); s(0) \le tse(31);

end process;

process(row value)

begin

if (row value = conv std logic vector(0, 10)) then

rowm1 <= conv_std_logic_vector(479, 10);</pre>

rowp1 <= conv std logic vector(1, 10);</pre>

elsif (row_value = conv_std_logic_vector(479, 10)) then

rowm1 <= conv std logic vector(478, 10);

rowp1 <= conv std logic vector(0, 10);

else

rowm1 <= row value - conv std logic vector(1, 10);

rowp1 <= row value + conv std logic vector(1, 10);

end if;

end process;

process(col value)

begin

if (col value = conv std logic vector(0, 10)) then

colm1 <= conv std_logic_vector(19, 10);</pre>

colp1 <= conv std logic vector(1, 10);</pre>

elsif (col value = \overline{conv} std logic vector(19, 10)) then

colm1 <= conv std logic vector(18, 10);</pre>

colp1 <= conv std logic vector(0, 10);</pre>

else

colm1 <= col value - conv std logic vector(1, 10);</pre>

colp1 <= col value + conv std logic vector(1, 10);</pre>

end if:

end process;

end synth life ram;

```

## mem\_controller.vhd

```

-- mem_controller.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This is the memory controller. It decides who between the

-- different components (life input, life calc, vga, image writer,

-- image reader, ram tester) gets to access the ram.

-- Every read/write is acknowledged (Note: for now the write

-- is acknowledged before (2 clock cycles) the write actually finishes).

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity mem controller is

port(clk: in std logic;

reset: in std logic;

ram_data: inout std_logic_vector(31 downto 0);

ram addr: out std logic vector(15 downto 0);

ram cs: out std logic;

ram we: out std logic;

ram swap: in std logic;

-- this allows us to

select which part in memory to use.

-- life input (WRITE)

life_input_write_req: in std_logic;

life_input_write_ack: out std_logic;

life input addr: in std logic vector(15 downto 0);

life input data: in std logic vector(31 downto 0);

-- img input (WRITE)

img input write req: in std logic;

img input write ack: out std logic;

img_input_addr: in std_logic_vector(15 downto 0);

img_input_data: in std_logic_vector(31 downto 0);

-- mem tester (READ)

mem_tester_read_req: in std_logic;

mem tester read ack: out std logic;

mem_tester_addr: in std_logic_vector(15 downto 0);

mem_tester_data: out std_logic_vector(31 downto 0);

```

```

-- life ram load (READ)

life_ram_load_read_req: in std_logic;

life ram load read ack: out std logic;

life ram load addr: in std_logic_vector(15 downto 0);

life ram load data: out std logic vector(31 downto 0);

- life ram save (WRITE)

life_ram_save_write_req: in std_logic;

life ram save write ack: out std logic;

life_ram_save_addr: in std_logic_vector(15 downto 0);

life_ram_save_data: in std_logic_vector(31 downto 0);

-- vga ram (READ)

vga_ram_read_req: in std_logic;

vga ram read without mem swap: in std logic;

vga ram read_ack: out std_logic;

vga_ram_addr: in std_logic_vector(15 downto 0);

vga_ram_data: out std_logic_vector(31 downto 0);

but2, but3: in std_logic);

end mem controller;

architecture synth_mem_controller of mem_controller is

type state is (init, w0, w1, w2, r0);

signal current_state, next_state: state;

signal buf_data: std_logic_vector(31 downto 0);

signal buf_addr: std_logic_vector(15 downto 0);

type load from is (none, life input, img input, life ram load, life ram save,

mem_tester, vga_ram);

signal current ram : std logic;

-- CONTROL SIGNALS

signal ctrl_buf: load_from;

begin

ram addr <= buf addr;</pre>

process(clk, reset)

begin

if (reset='1') then

current state <= init;</pre>

buf_{data} \leftarrow (others => '0');

buf addr <= (others => '0');

life_input_write_ack <= '0';</pre>

img_input_write_ack <= '0';</pre>

life ram save write ack <= '0';

mem_tester_read_ack <= '0';</pre>

life ram load read ack <= '0';

vga_ram_read_ack <= '0';</pre>

current ram <= '0';

elsif (clk'event and clk='1') then

current state <= next state;

life_input_write_ack <= '0';</pre>

img input write ack <= '0';

life_ram_save_write ack <= '0';</pre>

mem_tester_read_ack <= '0';</pre>

life ram load read ack <= '0';

vga ram read ack <= '0';

if (ram_swap = '1') then

current ram <= not(current ram);</pre>

end if;

case ctrl buf is

when img input =>

buf addr <= img input addr(15 downto 0);

buf_data <= img_input_data;</pre>

img input write ack <= '1';

when \overline{\text{life input}} = \overline{>}

buf addr <= current ram & life input addr(14 downto 0);</pre>

buf data <= life input data;</pre>

life_input_write_ack <= '1';</pre>

when life ram load =>

buf_addr <= current_ram & life_ram_load_addr(14 downto 0);</pre>

life_ram_load_read_ack <= '1';</pre>

when mem tester =>

if (but2 = '1') then

buf addr <= not(current ram) & mem tester addr(14 downto 0);</pre>

buf addr <= current ram & mem tester addr(14 downto 0);</pre>

```

```

end if;

mem tester read ack <= '1';</pre>

when life ram save =>

buf addr <= not(current ram) & life ram save addr(14 downto 0);

buf data <= life ram save data;</pre>

life ram save write ack <= '1';

when vga_ram =>

if (vga ram read without mem swap = '1') then

buf_addr <= vga_ram_addr(15 downto 0);</pre>

else

if (but3 = '1') then

buf_addr <= not(current_ram) & vga_ram_addr(14 downto 0);</pre>

buf addr <= current ram & vga ram addr(14 downto 0);</pre>

end if;

end if;

vga_ram_read_ack <= '1';</pre>

when others => null;

end case;

end if;

end process;

process(current state, img input write req, life input write req, mem tester read req,

life_ram_load_read_req, life_ram_save_write_req,

buf addr, buf data, ram data, vga ram read req)

begin

mem_tester_data <= "00100010001000100010001000100010";</pre>

-- this data should

life ram load data <= "0010001000100010001000100010"; -- never be used.

vga ram data <= "0010001000100010001000100010"; -- never be used.

ram cs <= '0';

ram we <= '0';

ctrl_buf <= none;

case current state is

when init =>

ram data <= (others => 'Z');

if (life input write req = '1') then

ctrl buf <= life_input;

next_state <= w0;</pre>

elsif (img_input_write_req = '1') then

ctrl buf <= img_input;</pre>

next state \leq w0;

elsif (mem\_tester\_read\_req = '1') then

ctrl_buf <= mem_tester;

next state <= r\overline{0};

elsif (life_ram_load_read_req = '1') then

ctrl buf <= life ram load;

next state <= r0;

elsif (life ram save write req = '1') then

ctrl buf <= life_ram_save;

next_state <= w0;</pre>

elsif (vga ram read req = '1') then

ctrl_buf <= vga_ram;

next state <= r0;

else

next state <= init;</pre>

end if;

when w0 =>

ram data <= buf data;

ram cs <= '1';

ram we <= '1';

next state <= w1;</pre>

when w1 =>

ram data <= buf data;

ram cs <= '1';

ram_we <= '1';

next state <= w2;

when w2 =>

ram data <= buf data;

ram cs <= '1';

```

```

ram we <= '1';

next state <= init;</pre>

when r0 =>

mem tester data <= ram data;</pre>

life ram load data <= ram data;

vga_ram_data <= ram_data;

ram cs <= '1';

next state <= init;</pre>

end case;

end process;

end synth mem controller;

mem tester.vhd

```

```

-- mem tester.vhd

-- Coded by Alok Menghrajani & Peter Amrhyn

-- This is a component to test the memory.

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_arith.all;

use ieee.std logic unsigned.all;

entity mem_tester is

port(clk: in std logic;

reset: in std_logic;

-- when this signal is set to 1, the mem tester

debug_start: in std_logic;

will start dumping the memory.

mem_tester_read_req: out std logic;

mem tester read ack: in std logic;

mem_tester_addr: out std_logic_vector(15 downto 0);

mem_tester_data: in std_logic_vector(31 downto 0);

byte send done: in std logic;

byte send data: out std logic vector(7 downto 0);

byte sending: out std logic);

end mem tester;

architecture synth mem tester of mem tester is

component counter is

port(clk: in std logic;

reset: in std logic;

inc: in std logic;

data: in std logic vector(9 downto 0);

timeout: out std logic;

value: out std logic vector(9 downto 0));

end component;

type state is (init, waiting, fetching, newline);

signal current state, next state: state;

signal counter1 timeout, counter2 timeout: std logic;

signal counter1_value, counter2_value, counter1_data, counter2_data: std_logic vector(9

downto 0);

-- CONTROL SIGNALS

signal ctrl_inc1, ctrl_inc2: std_logic;

-- mem tester ram req

-- rs232_send_byte_req

-- counter1 is the number of memory cols to display

-- counter2 is the number of memory lines (rows) to display

counter1_data <= conv_std_logic_vector(5, 10);</pre>

counter2_data <= conv_std_logic_vector(5, 10);</pre>

mem tester addr <= "00" & counter2 value(8 downto 0) & counter1 value(6 downto 2);</pre>

process(clk, reset)

begin

if (reset = '1') then

current state <= init;</pre>

elsif (clk'event and clk='1') then

current state <= next state;

end if;

end process;

```

```

counter1_unit: counter port map (clk => clk, reset => reset, inc => ctrl inc1, data =>

counter1 data, timeout => counter1 timeout,

value => counter1 value);

counter2 unit: counter port map (clk => clk, reset => reset, inc => ctrl inc2, data =>

counter2 data, timeout => counter2_timeout,

value => counter2 value);

-- the byte to send will depend on the 2 lower bits of counter1

process(counter1_value, mem_tester_data)

if (counter1_value(1 downto 0) = "11") then

byte send data <= mem tester data(7 downto 0);</pre>